7. INDEPENDENT STUDY PROJECT PRESENTATIONS

37

May 29

May 29

Final Class

Mandatory Attendance

Mandatory Attendance

36

May 27

May 27

Mandatory Attendance

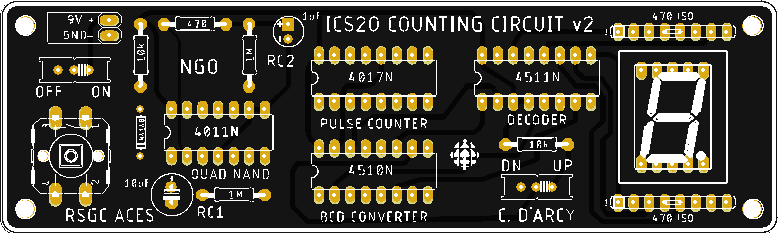

6. A COUNTING CIRCUIT

35

May 23

May 23

34

May 21

May 21

33

May 16

May 16

Binary Game Finals @ 1:15

WT vs DC

A Counting Circuit

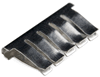

E. Binary Coded Decimal (BCD) Decoder

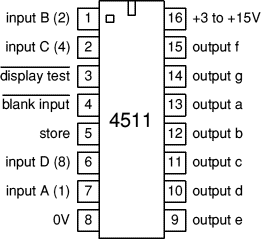

The 4511 BCD to 7-Segment Decoder

F. Seven-Segment Display

WT vs DC

A Counting Circuit

E. Binary Coded Decimal (BCD) Decoder

The 4511 BCD to 7-Segment Decoder

F. Seven-Segment Display

32

May 14

May 14

A Counting Circuit

D. Decimal Counting

Binary Up/Down Counter (4510)

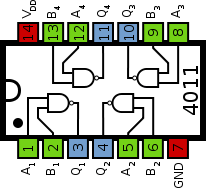

The 4516 Up/Down (0-15) Counter

D. Decimal Counting

Binary Up/Down Counter (4510)

The 4516 Up/Down (0-15) Counter

31

May 10

May 10

A Counting Circuit

C. Decade Counter (4017)

NGO Square Wave Output as Clock Input

to our FIRST Specialized IC:

The 4017 Decade Counter

C. Decade Counter (4017)

NGO Square Wave Output as Clock Input

to our FIRST Specialized IC:

The 4017 Decade Counter

30

May 8

May 8

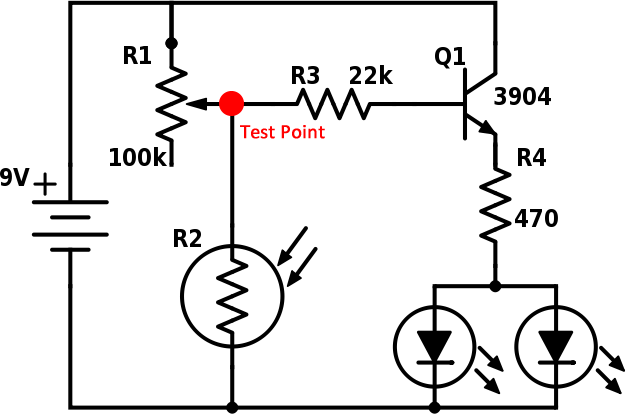

A Counting Circuit

B. NAND Gate Oscillator (4011) Part 2

Animations: TP3, RC Drain

Explore changes to RC2 components

B. NAND Gate Oscillator (4011) Part 2

Animations: TP3, RC Drain

Explore changes to RC2 components

29

May 6

May 6

28

May 2

May 2

5. DIGITAL FUNDAMENTALS, LOGIC GATES, and INTEGRATED CIRCUITS (ICs)

27

Apr 30

Apr 30

p. 45

What is the difference between

Vcc, Vdd, Vee, Vss, etc?

Digital Name Pairs, The Binary Number System

Number Systems: Binary (2)

Octal (8), Decimal (10), Hexadecimal (16) Binary Representation of Characters:

ASCII Table, Unicode

Vcc, Vdd, Vee, Vss, etc?

Digital Name Pairs, The Binary Number System

Number Systems: Binary (2)

Octal (8), Decimal (10), Hexadecimal (16) Binary Representation of Characters:

ASCII Table, Unicode

26

Apr 26

Apr 26

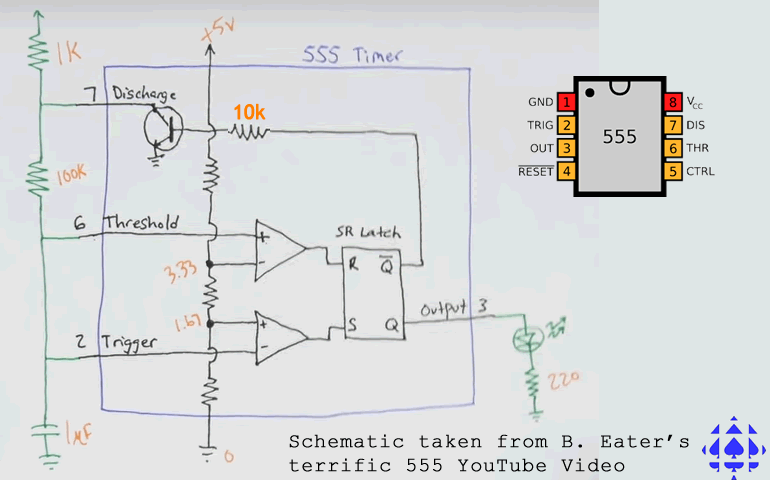

Best 555 Tutorial

on the Web...

![]() Eater's Astable 555

Eater's Astable 555

Note: Section 2 misses this one :(

Operational Amplifiers

As Comparator: p.71

FALSTAD: 555 Simulation

(Circuits > 555 Timer > Square Wave Generator)

25

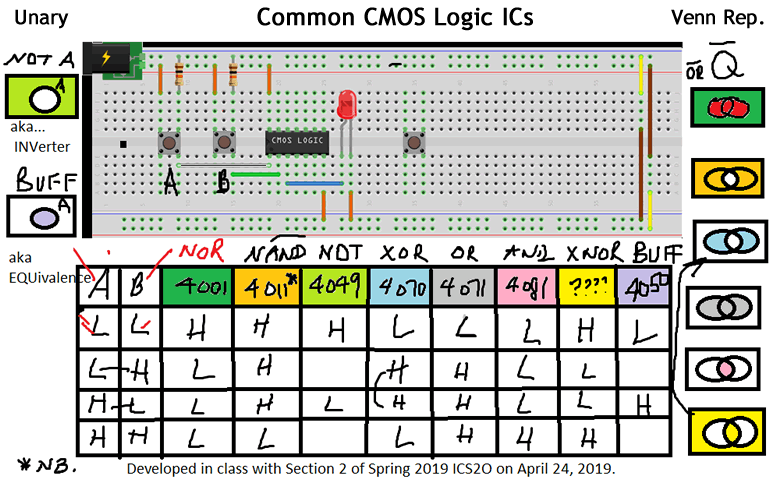

April 24

April 24

Review of Truth Tables

Combinational Logic Activities:

FALSTAD: Logic Gate IC Circuits

Multiple Input Gates

Gates as Operators: Boolean Arithmetic

The eXclusive OR (XOR) Gate

Activity. Addition-Related Logic Circuits

Combinational Logic Activities:

FALSTAD: Logic Gate IC Circuits

Multiple Input Gates

Gates as Operators: Boolean Arithmetic

The eXclusive OR (XOR) Gate

Activity. Addition-Related Logic Circuits

24

April 18

April 18

p. 47-48

![]()

![]()

![]()

![]()

![]()

23

April 16

April 16

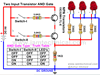

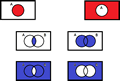

Transition from...

ANALOG (Continuous) to DIGITAL (Discrete):

Boolean Algebra and Venn Diagrams

Activity: Transistors as Logic Gates (TTL)

ANALOG (Continuous) to DIGITAL (Discrete):

Boolean Algebra and Venn Diagrams

Activity: Transistors as Logic Gates (TTL)

4. TRANSISTORS

21

April 12

April 12

20

April 10

April 10

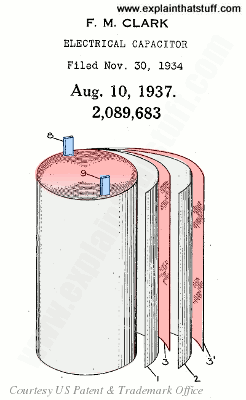

pp. 33-36

19

April 8

April 8

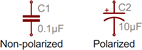

3. CAPACITORS

18

Apr 4

Apr 4

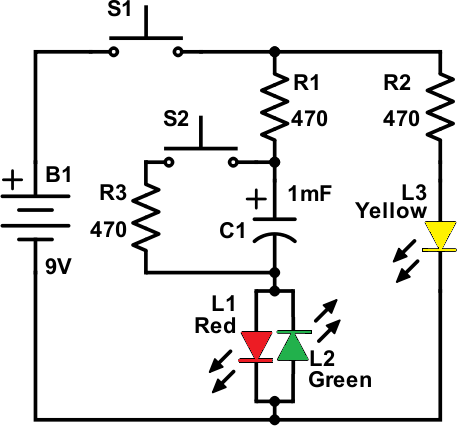

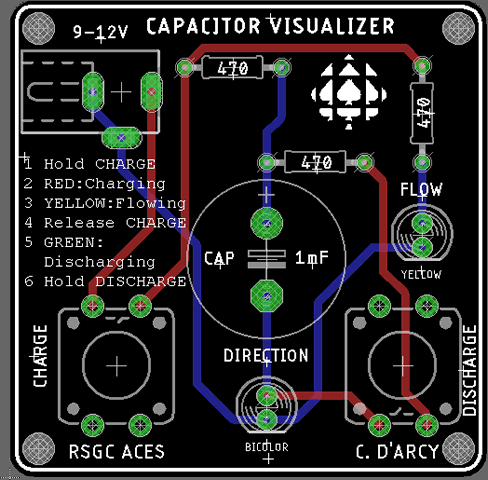

Project 2. The Capacitor Visualizer

Soldering and Assembly Stage

N. Vassos'

N. Vassos'

The Capacitor Visualizer

Soldering Tutorial

Soldering and Assembly Stage

The Capacitor Visualizer

Soldering Tutorial

17

Apr 2

Apr 2

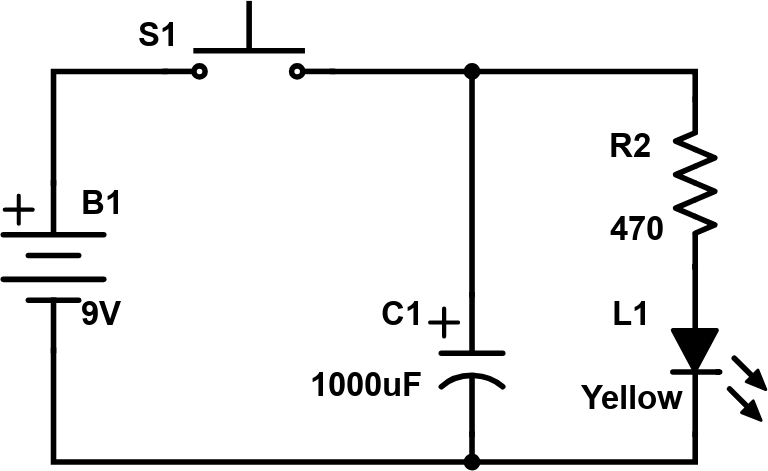

Project 2. The Capacitor Visualizer

Prototype and Time Trials Stage

Prototype and Time Trials Stage

16

Mar 29

Mar 29

15

Mar 27

Mar 27

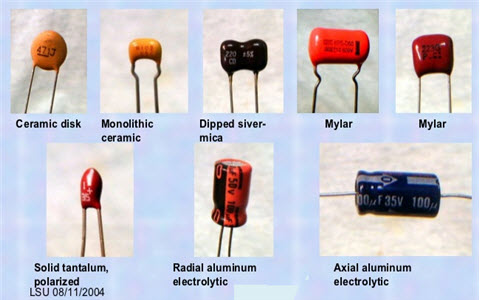

The Underlying Principle of Digital Logic:

Pull-Down and Pull-Up Resistor Configurations

LOGIC Functions: OR, AND

Diode-Resistor Logic (DRL)

Pull-Down and Pull-Up Resistor Configurations

LOGIC Functions: OR, AND

Diode-Resistor Logic (DRL)

Michael Faraday

2. DESIGN, DIVIDERS, DEVICES and DATASHEETS

14

Mar 7

Mar 7

CB HD* JL MM* TP

JR OS CT* WT HV* JW

CB FB* DC AG EL RM

LO* BS* LT* MT MvD*

ACES' ER Technical Writing: Don'ts and Dos

Use of the Active Voice

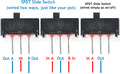

Manual Input Devices:

Buttons: PBNO, PBNC

Switches (SPST, SPDT, DPDT)

Activities: Switch Circuit

Rocket Launch: RocketLaunchQuestion.fzz

Use of the Active Voice

Manual Input Devices:

Buttons: PBNO, PBNC

Switches (SPST, SPDT, DPDT)

Activities: Switch Circuit

Rocket Launch: RocketLaunchQuestion.fzz

Buttons and Switches

13

Mar 5

Mar 5

12

Mar 1

Mar 1

Review TEL3M FC

Feedback Emails

ACES' Frame Player:

Field Forms

Field Forms

11

Feb 27

Feb 27

10

Feb 25

Feb 25

1. SIGNALS, SUPPLY, SYMBOLS, and SCHEMATICS

9

Feb 21

Feb 21

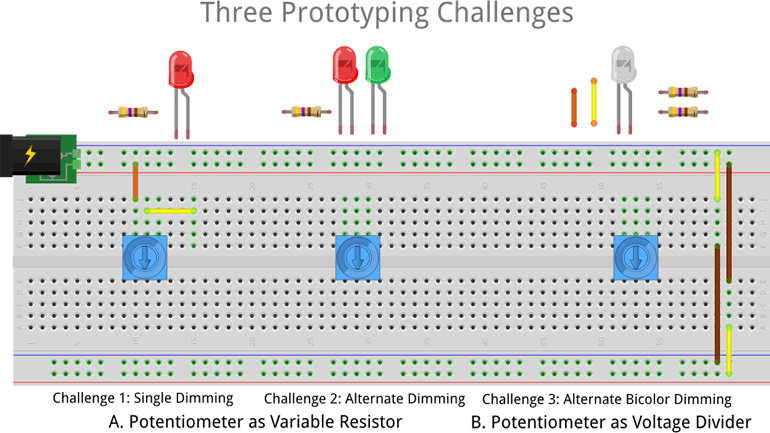

Introduction to Variable Resistors

Mechanical Potentiometers

Light-Dependent Resistors (LDRs)

Heat-Dependent Resistors (Thermistors)

Force-Sensitive Resistors (FSRs)

8

Feb 19

Feb 19

Waterfall Model (Continued)

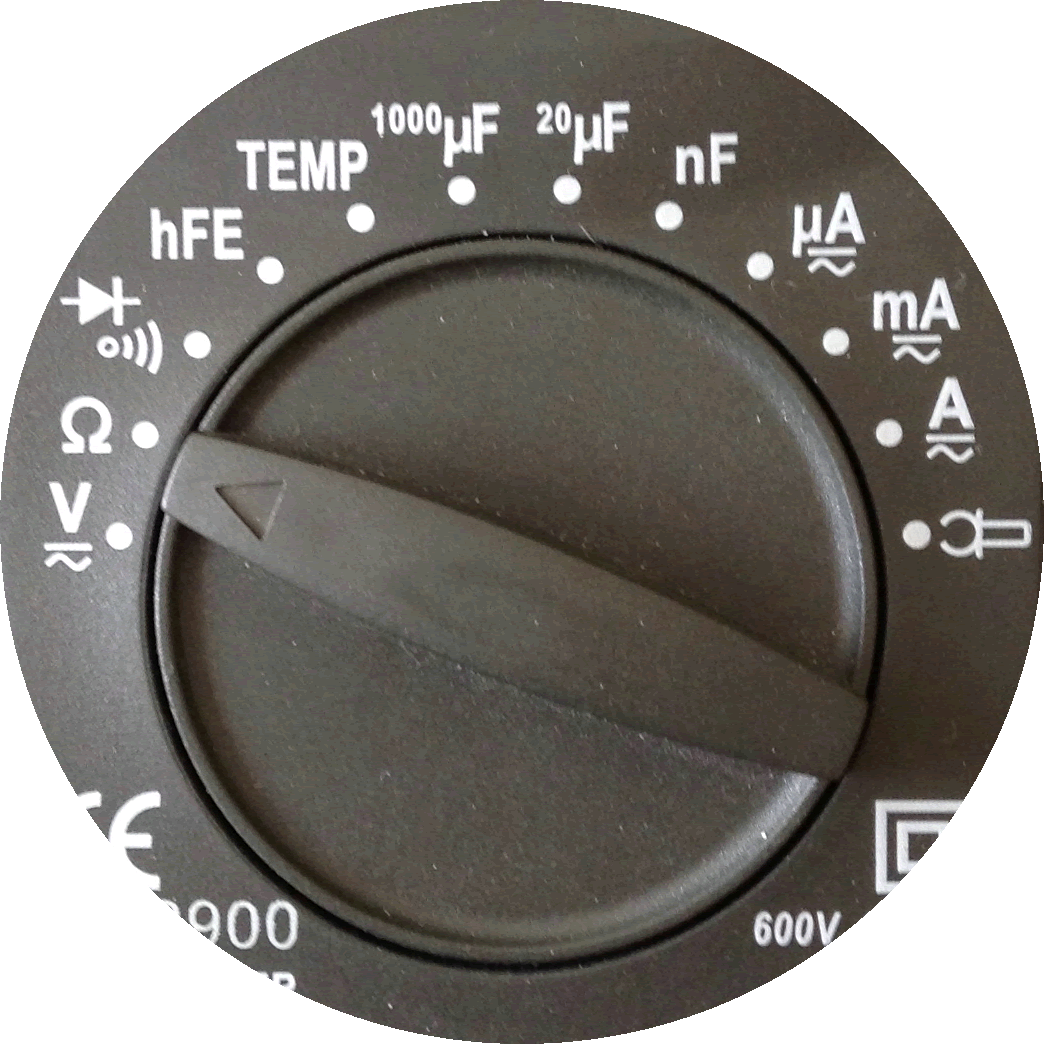

DMM: Measuring Voltage and Amperage

Circuit Analysis: Resistor Circuit

Circuit Analysis: Resistor Circuit

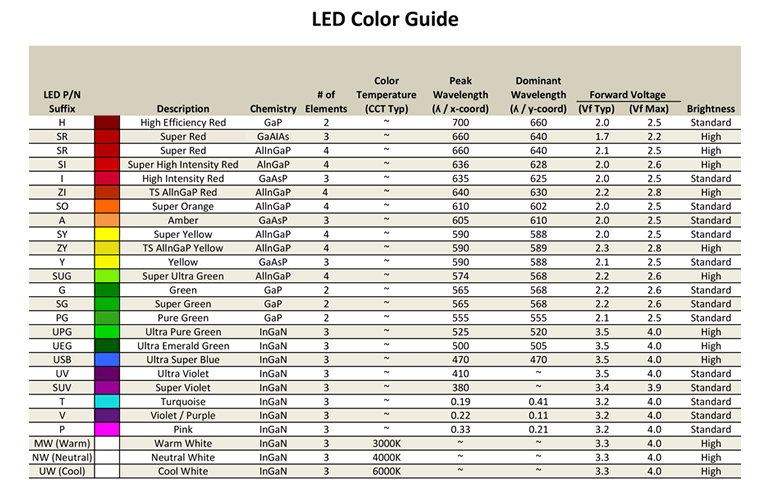

Circuit Analysis: LED Circuit

Circuit Analysis: LED Circuit

DMM: Measuring Voltage and Amperage

7

Feb 13

Feb 13

Introduction to VOLTAGE

Waterfall Model of a Closed Circuit

Fundamental Circuit Laws:

KVL: Kirchhoff's Voltage Law, `V=IR`, `P=IV`

Waterfall Model of a Closed Circuit

Fundamental Circuit Laws:

KVL: Kirchhoff's Voltage Law, `V=IR`, `P=IV`

6

Feb 11

Feb 11

`R_E=R_1+R_2`

`1/R_E=1/R_1+1/R_2`

`1/R_E=1/R_1+1/R_2`

Analysis of Fixed Resistors in Series and Parallel

Concept of: Equivalent Resistance (`R_E`)

Concept of: Equivalent Resistance (`R_E`)

5

Feb 7

Feb 7

Voltage: `V=IR`

Power: `P=IV`

Power: `P=IV`

4

Feb 5

Feb 5

Digital Multimeter (DMM)

Circuit Symbols, Reading a Schematic

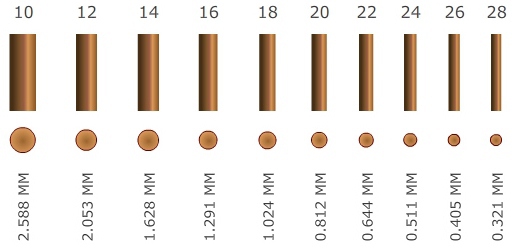

Useful Resistor Circuits, Wire Ampacity

3

Feb 1

Feb 1

Direction of Current, Anode and Cathode

Power: `P=IxxV`

Increased Power

Wire Gauge (p. 77), Greek Alphabet (p. 78)

Fixed (Current-Limiting) Resistors

Power: `P=IxxV`

Increased Power

Wire Gauge (p. 77), Greek Alphabet (p. 78)

Fixed (Current-Limiting) Resistors

2

Jan 30

Jan 30

Discussion:

What is Electricity?

The Atom, Signals, Water Analogy, Flow Models

Giants of Electricity (p.81)

Supply: Voltage, Current (Direct and Alternating)

Direction of Current, Resistance

Circuit Symbols and Schematics

Reading a Schematic, Simple Resistor Circuits

Ben Eater: How Semiconductors Work

Ben Eater: How Semiconductors Work

The Atom, Signals, Water Analogy, Flow Models

Giants of Electricity (p.81)

Supply: Voltage, Current (Direct and Alternating)

Direction of Current, Resistance

Circuit Symbols and Schematics

Reading a Schematic, Simple Resistor Circuits

Master of Lightning

1b

Jan 28

Jan 28

Student Reflections

Why is this Course Necessary? The Workbook?

Technical Advisors, Acknowledgements

ACES: A Focus on Skills, Table of Contents

Why is this Course Necessary? The Workbook?

Technical Advisors, Acknowledgements

ACES: A Focus on Skills, Table of Contents

1a

Jan 28

Jan 28

REPUTATION and RESPECT

RSGC ACES CULTURE: Taking a

Short, Medium, and Long Term View

of your Futures

ACES Hall of Fame:

E. McAulliffe ('18), Mariano Elia ('15), Jack Gettings ('10)

RSGC ACES CULTURE: Taking a

Short, Medium, and Long Term View

of your Futures

ACES Hall of Fame:

E. McAulliffe ('18), Mariano Elia ('15), Jack Gettings ('10)

[ACES Culture]