7. INDEPENDENT STUDY PROJECT

39

Jan 18

Jan 18

Final Hardware Class

38

Jan 16

Jan 16

37

Jan 14

Jan 14

36

Jan 10

Jan 10

Work Period

35

Jan 8

Jan 8

34

Dec 18

Dec 18

オープンソースでプログラムもできる、ニキシー管デジタル時計がアツい

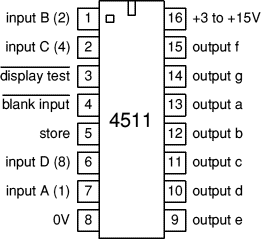

Decade Counter Output as Input

to our THIRD Specialized IC:

The 4511 BCD to 7-Segment Decoder

Fola's Version

Fola's Version

Decade Counter Output as Input

to our THIRD Specialized IC:

The 4511 BCD to 7-Segment Decoder

33

Dec 14

Dec 14

ISP Proposal Due

(handed to Mr. D at the START of the class)

Decade Counter Output as Clock Input

to our SECOND Specialized IC:

The 4516 Up/Down (0-15) Counter

(handed to Mr. D at the START of the class)

Decade Counter Output as Clock Input

to our SECOND Specialized IC:

The 4516 Up/Down (0-15) Counter

32

Dec 12

Dec 12

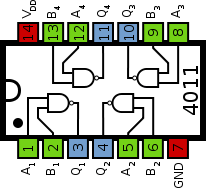

NGO Square Wave Output as Clock Input

to our FIRST Specialized IC:

The 4017 Decade Counter

RSGC ACES: Decade Counter

RSGC ACES: Decade Counter

to our FIRST Specialized IC:

The 4017 Decade Counter

31

Dec 10

Dec 10

ISP Proposal

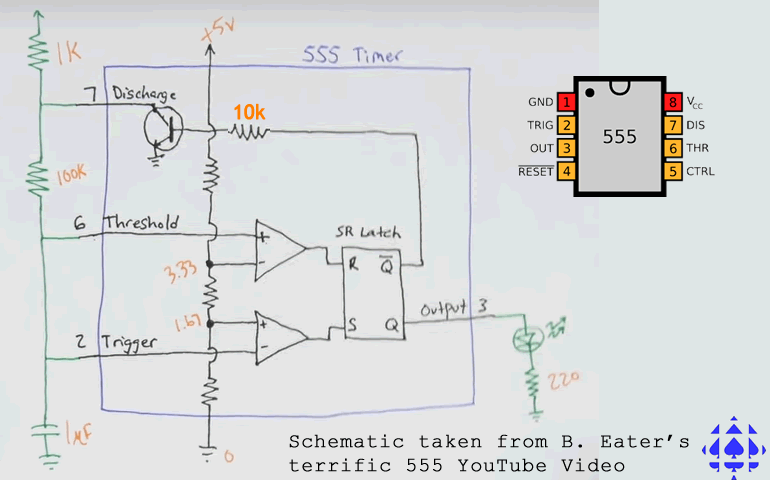

555 Tutorials: #1, #2

(you want Astable mode)

LM555 Datasheet

Fun 555 Circuits

555 Calculator

555 Tutorials: #1, #2

(you want Astable mode)

LM555 Datasheet

Fun 555 Circuits

555 Calculator

Best 555 Tutorial

on the Web...

![]() Eater's Astable 555

Eater's Astable 555

Logic Gates as

Memory (latch, flipflop) Elements

SR > D > FlipFlop

SR > D > FlipFlop

Combination vs Sequential Logic Circuits: p.70

Comparators

Operational Amplifiers (OpAmps): p.71

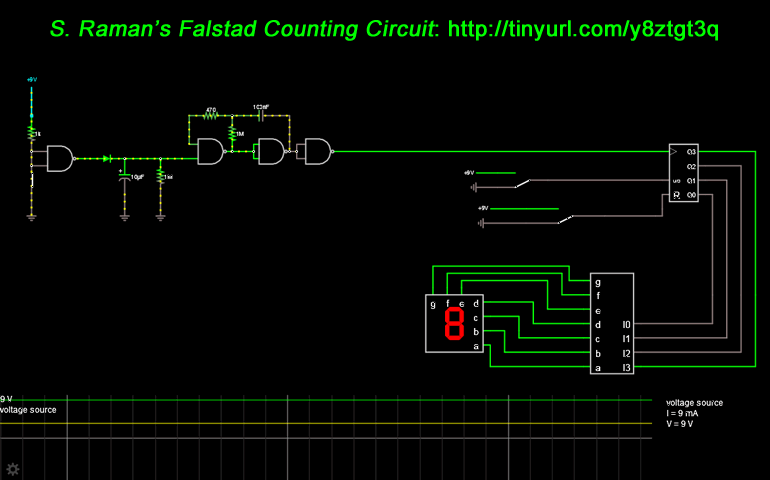

FALSTAD: 555 Simulation

(Circuits > 555 Timer > Square Wave Generator)

Memory (latch, flipflop) Elements

Combination vs Sequential Logic Circuits: p.70

Comparators

Operational Amplifiers (OpAmps): p.71

FALSTAD: 555 Simulation

(Circuits > 555 Timer > Square Wave Generator)

30

Dec 6

Dec 6

The NAND Gate Oscillator (NGO)

Activity. NGO Part 2

Animations: TP3, RC Drain

Activity: NGO Part 3 Fola's Version

Fola's Version

Activity. NGO Part 2

Animations: TP3, RC Drain

Activity: NGO Part 3

29

Dec 4

Dec 4

5. INTEGRATED CIRCUITS (ICs) I: DIGITAL LOGIC GATES

28

Nov 30

Nov 30

27

Nov 28

Nov 28

Combinational Logic Activties:

FALSTAD: Logic Gate IC Circuits

Multiple Input Gates

Gates as Operators: Boolean Arithmetic

The eXclusive OR (XOR) Gate

Activity. Addition-Related Logic Circuits

FALSTAD: Logic Gate IC Circuits

Multiple Input Gates

Gates as Operators: Boolean Arithmetic

The eXclusive OR (XOR) Gate

Activity. Addition-Related Logic Circuits

26

Nov 26

Nov 26

Activity: Single input (Unary) Logic Gates

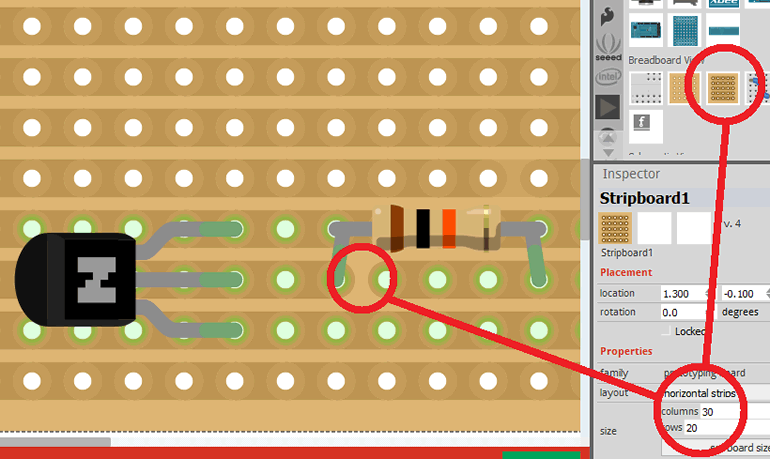

Breadboarding Tips for ICs

Breadboarding Tips for ICs

25

Nov 22

Nov 22

p. 47-48

Role of Venn Diagrams

Digital Logic Gates - Truth Tables

4. DIGITAL FUNDAMENTALS

24

Nov 20

Nov 20

Signed Binary:

The

2's Complement

Algorithm

The

2's Complement

Algorithm

Number Systems:

Binary (2)

Octal (8), Decimal (10), Hexadecimal (16)

Binary Representation of Characters:

ASCII Table, Unicode

Octal (8), Decimal (10), Hexadecimal (16)

Binary Representation of Characters:

ASCII Table, Unicode

23

Nov 14

Nov 14

p. 45

What is the difference between

Vcc, Vdd, Vee, Vss, etc?

Digital Name Pairs, The Binary Number System

Vcc, Vdd, Vee, Vss, etc?

Digital Name Pairs, The Binary Number System

22

Nov 8

Nov 8

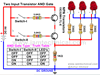

Activity: Transistors as Logic Gates (TTL)

Venn Diagram of Number Sets...

Integers, Place Value

Analog (Continuous) vs Digital (Discrete)

Review of the Decimal Number System

Venn Diagram of Number Sets...

Integers, Place Value

Analog (Continuous) vs Digital (Discrete)

Review of the Decimal Number System

3. TRANSISTORS

21

Nov 6

Nov 6

2N3904 Datasheet

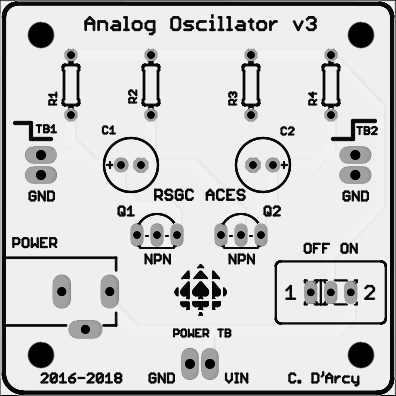

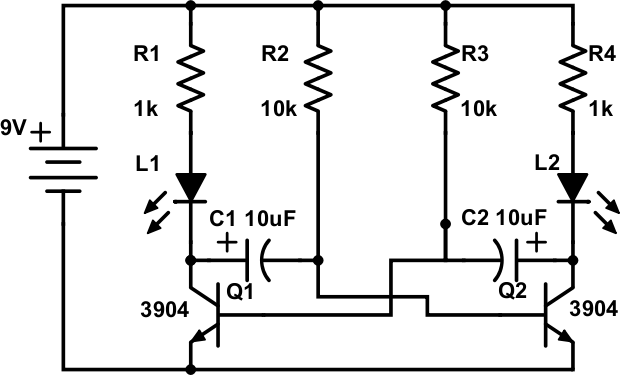

Build Session:

Project 3. The Analog Oscillator

Falstad: Analog Oscillator Simulation

RSGC ACES: Astable Multivibrator

RSGC ACES: Astable Multivibrator

Research: The Astable Multivibrator

Build Session:

Project 3. The Analog Oscillator

Falstad: Analog Oscillator Simulation

Research: The Astable Multivibrator

For Successful Builds...the early

Distribution of Additional Analog Oscillator Parts

The Analog Oscillator

20

Nov 2

Nov 2

Project 2. The Capacitor Visualizer

(due tomorrow)

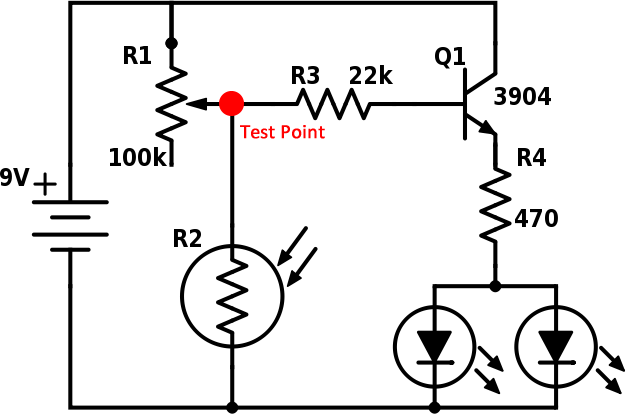

Recall Diode-Resistor Logic...

Transistor-Transistor Logic: AND, OR

Transistor Testing

Review/Discussion of Transistor Circuits

(due tomorrow)

Recall Diode-Resistor Logic...

Transistor-Transistor Logic: AND, OR

Transistor Testing

Review/Discussion of Transistor Circuits

19

Oct 31

Oct 31

18

Oct 29

Oct 29

2. DESIGN, DIVIDERS, DEVICES and DATASHEETS

17

Oct 25

Oct 25

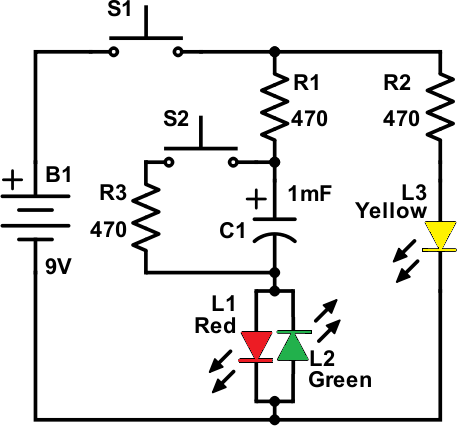

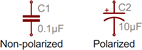

Prototype Project 2. The Capacitor Visualizer

Begin to conduct required time trials

Solder long leads to your

PBNO, PBNC and Potentiometer

Solder your *NEW* DC Breakout Board

16

Oct 23

Oct 23

Review of Voltage Division Feedback Email

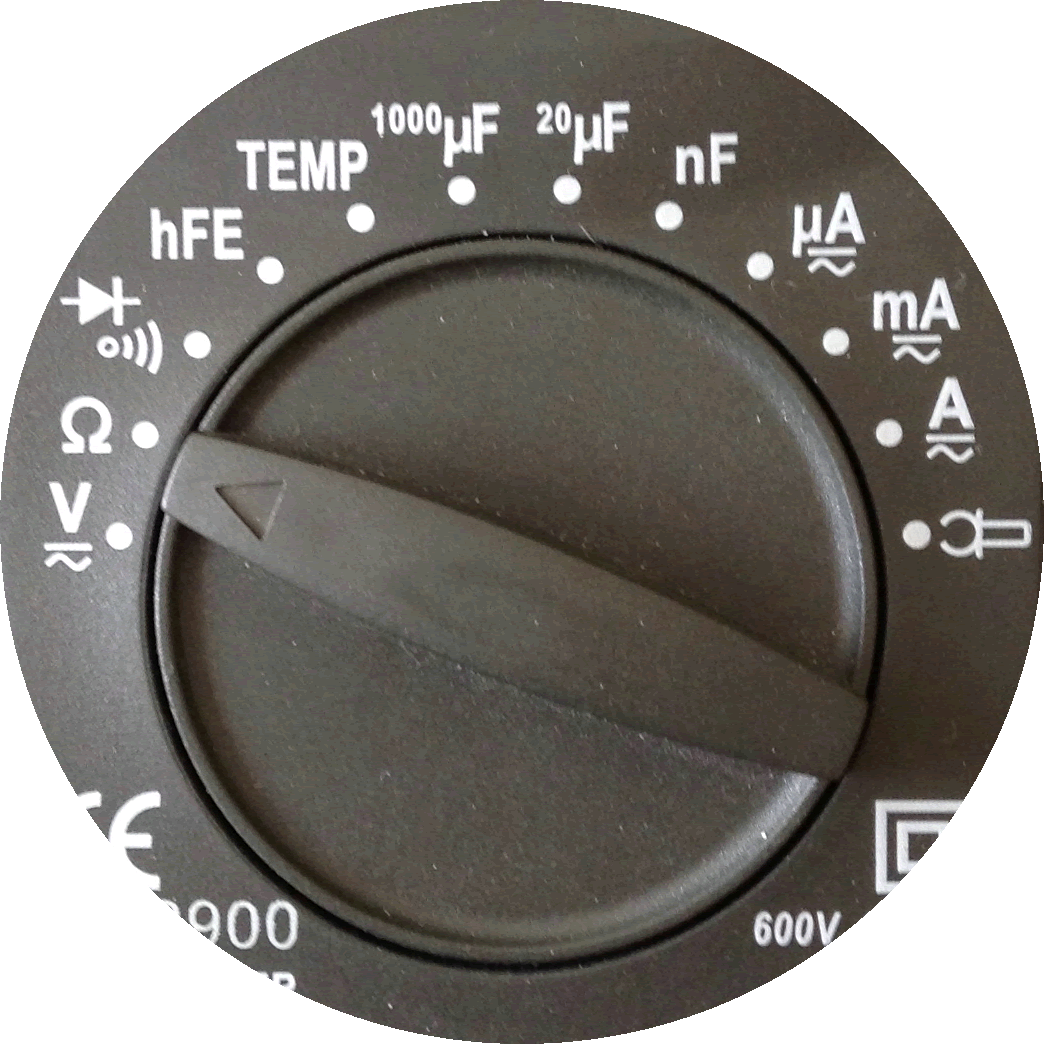

Measuring Capacitance with the DMM

Review Capacitor Circuits on page 32

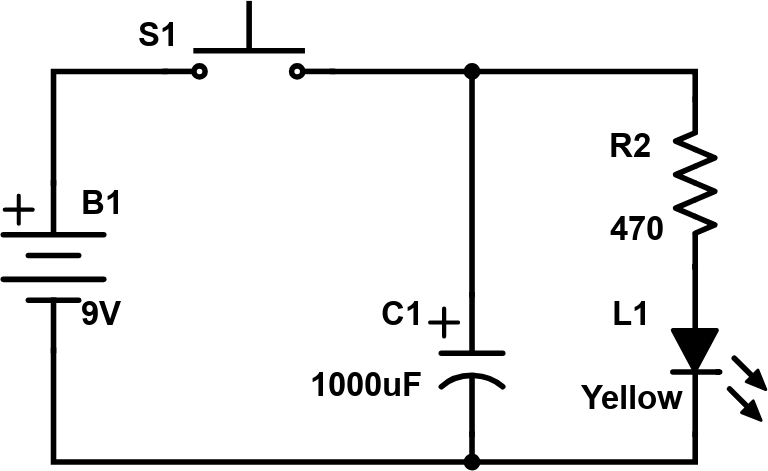

Prototype the circuit to the left...

...and then the rollover modification

Capacitors as Timers: `tau = R times C`

Measuring Capacitance with the DMM

Review Capacitor Circuits on page 32

Prototype the circuit to the left...

...and then the rollover modification

Capacitors as Timers: `tau = R times C`

SA, AB, MC, ZC, JG,

JK, LL, TM, HM, AM,

LRC, JTP, ET**, KT, RT,

JV, NWS

JBe, PB, JBu*, PC, JD*,

CG, MJ, SR, JS, LW

15

Oct 19

Oct 19

14

Oct 17

Oct 17

The Underlying Principle of Digital Logic:

Pull-Down and Pull-Up Resistor Configurations

LOGIC Functions: OR, AND

Diode-Resistor Logic (DRL)

Pull-Down and Pull-Up Resistor Configurations

LOGIC Functions: OR, AND

Diode-Resistor Logic (DRL)

13

Oct 15

Oct 15

ACES' ER Technical Writing: Don'ts and Dos

Use of the Active Voice

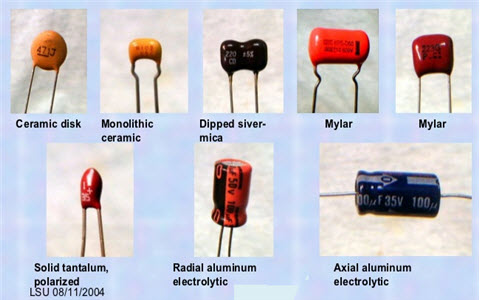

Manual Input Devices:

Buttons: PBNO, PBNC

Switches (SPST, SPDT, DPDT)

Activities: Switch Circuit

Rocket Launch: RocketLaunchQuestion.fzz

Use of the Active Voice

Manual Input Devices:

Buttons: PBNO, PBNC

Switches (SPST, SPDT, DPDT)

Activities: Switch Circuit

Rocket Launch: RocketLaunchQuestion.fzz

Buttons and Switches

12

Oct 11

Oct 11

Review TEL3M FC

Feedback Emails

Open House

(Period 2)

(Period 2)

11

Oct 9

Oct 9

10

Oct 4

Oct 4

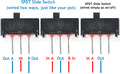

The Two Roles of the Potentiometer:

Variable Resistor and Voltage Divider

Two Sample Circuits to Demonstrate the two Roles

Variable Resistor and Voltage Divider

Two Sample Circuits to Demonstrate the two Roles

1. SIGNALS, SUPPLY, SYMBOLS, and SCHEMATICS

9b

Oct 2

Oct 2

Summary of:

Signals, Supply, Symbols, and Schematics

Signals, Supply, Symbols, and Schematics

9a

Oct 2

Oct 2

Introduction to Variable Resistors

Mechanical Potentiometers

Light-Dependent Resistors (LDRs)

Heat-Dependent Resistors (Thermistors)

Force-Sensitive Resistors (FSRs)

8

Sep 28

Sep 28

Waterfall Model (Continued)

The Concept of Voltage Division

DMM: Measuring Voltage and Amperage

Circuit Analysis

Circuit Analysis

The Concept of Voltage Division

DMM: Measuring Voltage and Amperage

7

Sep 26

Sep 26

Introduction to VOLTAGE

Waterfall Model of a Closed Circuit

Fundamental Circuit Laws:

KVL: Kirchhoff's Voltage Law, `V=IR`, `P=IV`

Waterfall Model of a Closed Circuit

Fundamental Circuit Laws:

KVL: Kirchhoff's Voltage Law, `V=IR`, `P=IV`

6

Sep 24

Sep 24

`R_E=R_1+R_2`

`1/R_E=1/R_1+1/R_2`

`1/R_E=1/R_1+1/R_2`

ACES' Frame Player:

Resistor Circuits

Resistor Circuits

Analysis of Fixed Resistors in Series and Parallel

Concept of: Equivalent Resistance (`R_E`)

Resistors.xlsx (...a little more math)

Resistors.xlsx (...a little more math)

Concept of: Equivalent Resistance (`R_E`)

5

Sep 19

Sep 19

Voltage: `V=IR`

Power: `P=IV`

Power: `P=IV`

Ohm's Law

Analysis of Single Resistor Circuit

Resistors.xlsx (...a little math)

Resistors.xlsx (...a little math)

4

Sep 17

Sep 17

3

Sep 13

Sep 13

1-11

Direction of Current, Anode and Cathode

Power: `P=IxxV`

Wire Gauge (p. 77), Greek Alphabet (p. 78)

Fixed (Current-Limiting) Resistors

Power: `P=IxxV`

Wire Gauge (p. 77), Greek Alphabet (p. 78)

Fixed (Current-Limiting) Resistors

2

Sep 11

Sep 11

Discussion:

What is Electricity?

The Atom, Signals, Water Analogy, Flow Models

Giants of Electricity (p.81)

Supply: Voltage, Current (Direct and Alternating)

Direction of Current, Resistance

Circuit Symbols and Schematics

Reading a Schematic, Simple Resistor Circuits

How Semiconductors Work

How Semiconductors Work

The Atom, Signals, Water Analogy, Flow Models

Giants of Electricity (p.81)

Supply: Voltage, Current (Direct and Alternating)

Direction of Current, Resistance

Circuit Symbols and Schematics

Reading a Schematic, Simple Resistor Circuits

1b

Sep 7

Sep 7

Distribute Workbook

and Toolkit

and Toolkit

Student Reflections

Why is this Course Necessary? The Workbook?

Technical Advisors, Acknowledgements

ACES: A Focus on Skills, Table of Contents

1a

Sep 7

Sep 7

REPUTATION and RESPECT

RSGC ACES CULTURE: Taking a

Short, Medium, and Long Term View

of your Futures

ACES Hall of Fame:

E. McAulliffe ('18), Mariano Elia ('15), Jack Gettings ('10)

RSGC ACES CULTURE: Taking a

Short, Medium, and Long Term View

of your Futures

ACES Hall of Fame:

E. McAulliffe ('18), Mariano Elia ('15), Jack Gettings ('10)

[ACES Culture]