There are no quizzes, tests, or exams in our ACES program. Put another way, you are NEVER put into the position of having a dramatically limited amount of time to demonstrate the skills you have acquired. You can invest as much (or as little) time into your reports as you choose. In return for being granted complete control over the depth and quality of your submissions I can place a premium on detail, precision, and the pursuit of perfection. So, my advice to you if you want to become exceptional is to follow the written and oral instructions carefully and, beyond the required elements of each report, demonstrate tasteful and appropriate creativity and imagination to distinguish yourself from the mediocre. Good luck and, remember, the race is long but it's over quickly.

There are no quizzes, tests, or exams in our ACES program. Put another way, you are NEVER put into the position of having a dramatically limited amount of time to demonstrate the skills you have acquired. You can invest as much (or as little) time into your reports as you choose. In return for being granted complete control over the depth and quality of your submissions I can place a premium on detail, precision, and the pursuit of perfection. So, my advice to you if you want to become exceptional is to follow the written and oral instructions carefully and, beyond the required elements of each report, demonstrate tasteful and appropriate creativity and imagination to distinguish yourself from the mediocre. Good luck and, remember, the race is long but it's over quickly.

Reports. Required Elements

If you do not submit your report by the deadline specified, you receive a mark of 0. This is done as a favour to you to help you appreciate that the real world will dismiss you if you can not demonstrate responsibility and accountability. You are to archive ALL of your reports in the single Word document, DER.docx. The first page is your Title page, followed by a multi-page Table of Contents, after which your reports begin. EACH report will start at the top of the next new page and, unless otherwise specified, consist of the following sections, in the order listed,

Purpose

Reference

Procedure

Media

Reflection

The vast majority of us can tell the difference between quality and rubbish in an instant. As a young scholar you have to decide what your name will stand for. It should matter very little whether you enjoy a task or not; if you're going to attach your name to something it is a direct reflection of who you are.

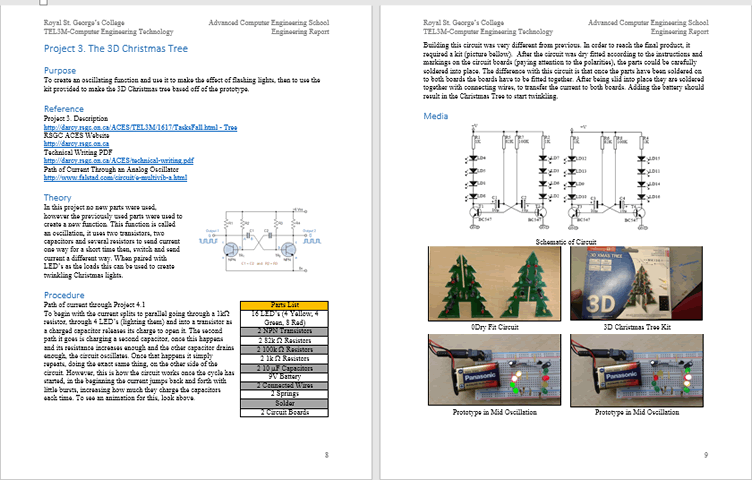

Project 1.3. The Counting Circuit

This final activity provides a simple introduction to fundamental capabilities of many digital devices: counting and display. There are a number of stages or subcircuits in this system and your DER will clearly present the role played by each.

This final activity provides a simple introduction to fundamental capabilities of many digital devices: counting and display. There are a number of stages or subcircuits in this system and your DER will clearly present the role played by each.

Start your DER with a big picture Theory section,

written in your own words that mentions, generally, the input to the system, the generation of a clock signal consisting of pulses having both a duration and a frequency, culminating in the presentation of the pulse count on the display device. This would an ideal place to present a detailed, margin-to-margin Fritzing diagram, breadboard or (organized) schematic view, to introduce your readers to the full prototype you are about to describe and discuss in three pages that follow.

A Note on Graphics. Graphics should support the text they are illuminating. Poorly composed photos, sloppy and inconsistent choices for diagrams like pinouts and schematics work against you as they can confuse your readers and leave them with a sense that the author doesn't care about his presentation so why should they?

Follow the Theory Section with the eight subsections (A-H) described below. For the first section, Analog Input, include, as a graphic, that part of the schematic that it pertains to. The next five sections (B-F) subsections should include a Reference Section that includes the respective live hyperlink appearing below:

Following the Reference Subsection within each of the five areas, include a Purpose section (this one could go before the Reference Section)

describing in detail, how each stage contributes to the sequence. Be sure to clearly present the input, processing, and output of each stage, supported by informative, attractive, and well-formatted graphics.

Following the final subsections include Media (captioned photos and video) and Reflection sections.

A. Button Input

- Purpose (discuss the momentary PBNO and its pullup resistor configuration)

- Include your own breadboard/schematic diagram, right-aligned, to

support your discussion.

B. NAND Gate Oscillator (4011)

- Purpose

- Explain, in detail, the function of this chip (Input, Processor, Output)

- Explain the concept of analog input to digital output and how this

chip accomplished this

- Include

a discussion of the pin diagram in this

IC

- Explain what a clock signal is

- Discuss the role played by RC1 and RC2 and the role played by its respective capacitors and resistors.

- Pinout diagram taken from the web and your own breadboard /schematic of the wiring and supportive analog components

C. Decade Counter (4017)

- Purpose

- Explain, in detail, the function of this chip (Input, Processor, Output)

- Explain what it means to ensure ALL of the input pins must be conditioned and

how this is done

- Explain why Pin 12 is referred to as the Divide-by-10 pin with respect to the input and output clock signals.

- Pinout diagram taken from the web and your own breadboard /schematic of the wiring.

D. Decimal Counting Binary Up/Down Counter (4510)

- Purpose

- Explain, in detail, the function of this chip (Input, Processor, Output)

- Create a two-column table with rows for all 16 4-bit binary values in the

left column and their equivalent decimal values in the right column

- Pinout diagram taken from the web

E. Binary Counting Decimal Decoder (4511)

- Purpose

- Explain, in detail, the function of this chip (Input, Processor, Output)

- Explain the purpose of the Blank, Store, and LampTest pins and how they must

be conditioned for normal use.

- Pinout diagram taken from the web

F. Seven-Segment Display

- Purpose

- Explain, in detail, the function of this component

- Explain the difference between the Common Anode (CA) and Common Cathode (CC)

versions of this component. Which one did we use?

- Explain how the pins on the 4511 and 7-seven segment make the wiring straightforward.

- Explain why each pin on the display requires its own resistor.

- Graphic (google a similar small image)

- Pinout diagram taken from the web

G. A Counting Circuit PCB

Update: See email post on Thursday December 17 to the ICS2O Conference regarding Stages G and H.

Soldering Advice and Tips for (Qualifying) Fall 2020 ICS2O-E ACES.

- The Hare lost. The Tortoise, on the other hand, read ALL the tips below before even thinking about beginning. He won.

- Watch N. Vassos' ACES' Soldering Video for some great tips. Watch it AGAIN even if you have seen it previously.

- DO NOT BE HASTY. Take your time with this and double-check with the Forum if you are not sure to avoid disappointment and a reduced mark for the careless.

- The supplementary parts shown in the photo below wil be mailed to qualified ACES on Monday December 21.

- In addition to these parts, you will need to supply 2-10 KΩ, 2-1 MΩ and 1 470 Ω fixed resistors from your inventory.

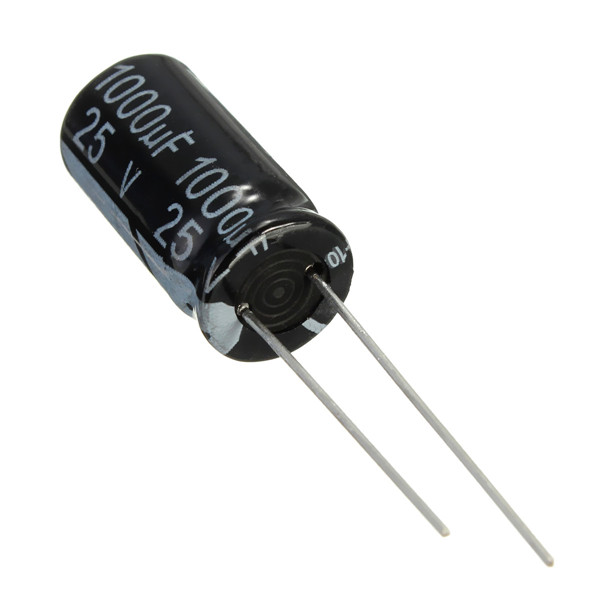

- In place of the 10 μF electrolytic capacitor, I have provided a compact 100 μF capacitor for longer duration.

- Your soldering pen should be no hotter that 300°C, and you should take no more than 3s per solder joint to avoid compromising your component.

- Reverse tweezers should be considered to hold components tight to the PCB when soldering upside down.

- Solder the smaller components first, working upwards to the larger ones.

- The IC Sockets (chip seats) have a notch in them. Orient them to match the silk screen notch. DO NOT SOLDER THE SOCKETS WITH THE IC IN THE SEAT. ICs are placed in the seat after soldering to avoid any exposure to heat.

- AFTER the IC Sockets are soldered, you can place your ICs in them (4011, 4017, 4510, 4511), ensuring the reference notches match the silk screening of the PCB (and, hopefully your sockets)

- Line up the resistor network so the dot matches the silk screen indication (left).

- Solder the 7-Segment Display in LAST. By this time you will be more relaxed and more confident. Remember, 3s per joint, max.

- DO NOT SOLDER a power connector/clip to the PCB as I'll provide a superior one with the case if this stage is successful.

- For the novice solderer (you), soldercan run into close, adjacent empty holes. Without the right equipment it can be almost impossible to remove it. For this reason, I STRONGLY urge you to consider placing the secondary component in its hole so that, if the solder runs, no problem, the part is already there!

- Finally, of the extra parts I have supplied only three of them did not come in your original kits (the PCB and the two resistor networks). I have chosen to give you replacements partly for esthetics, partly for performance (pricier kinked IC Sockets) and possibly because for possible loss or failure of the originals.

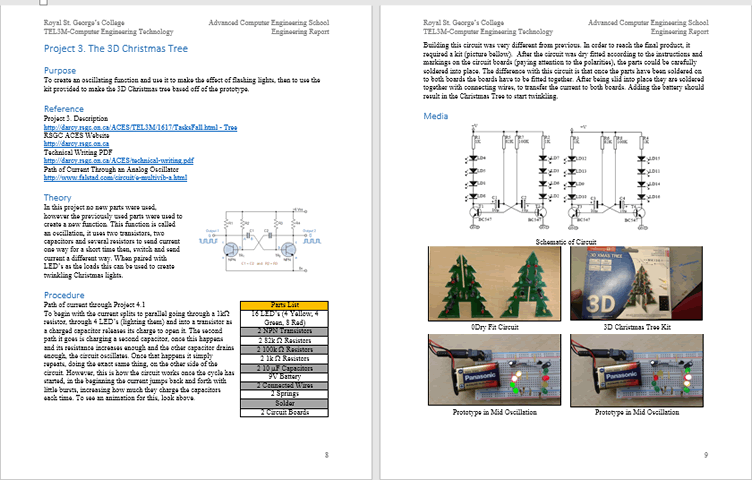

Once the prototype media has been obtained for your DER (photos and video), ACES wishing to extend their engineering skills are encouraged to convert their breadboard prototype to a more permanent device. A custom printed circuit board was designed and manufactured expressly for the use by Jr. ACES for this purpose. Interested ACES should present their working prototype to Mr. D'Arcy at least TWO days prior to the DER due date in order to receive their PCB. Receipt of such a board comes with the expectation that components will be soldered, the circuit tested, and summarized in text, photos, and video as part of the DER summary for this Counting Circuit project.

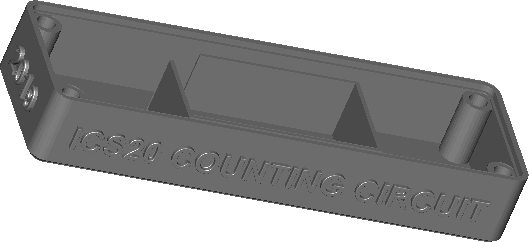

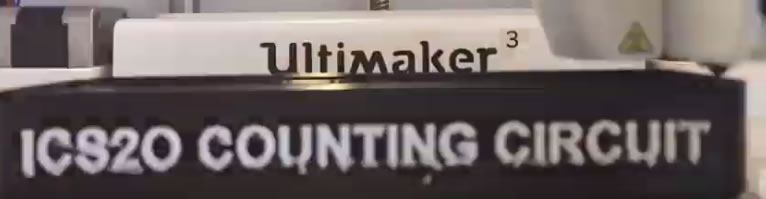

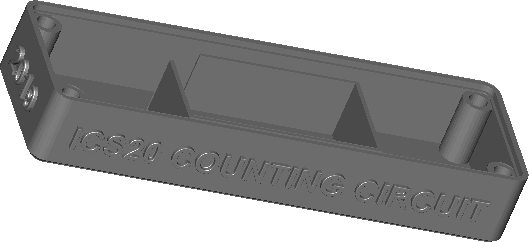

H. A Counting Circuit PCB Case

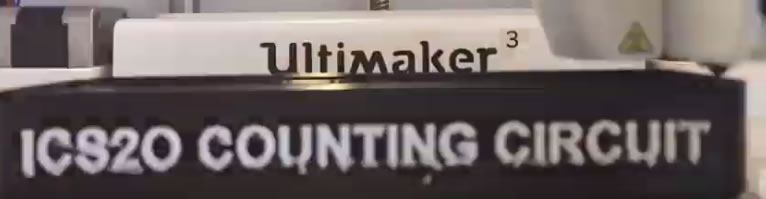

Congratulations on reaching the final stage (8) of our marathon Counting Circuit project! Students that have successfully soldered their PCBs that demonstrate forward (and backwards) counting on the seven-segment display are invited to present their circuit to Mr. D. to receive a custom case designed and printed in the DES by J. Dolgin (ACES '20) into which their device can be mounted. A similar two-colour case was printed on the Ultimaker 3 in 2018 by K. Fiset-Algarvio (ACES '19). Click the image below to view a short time-lapse video of the case being printed,

Congratulations on reaching the final stage (8) of our marathon Counting Circuit project! Students that have successfully soldered their PCBs that demonstrate forward (and backwards) counting on the seven-segment display are invited to present their circuit to Mr. D. to receive a custom case designed and printed in the DES by J. Dolgin (ACES '20) into which their device can be mounted. A similar two-colour case was printed on the Ultimaker 3 in 2018 by K. Fiset-Algarvio (ACES '19). Click the image below to view a short time-lapse video of the case being printed,

Power for the device is sourced from a 9V battery inside a compartment within the interior of the case. The leads of a battery snap can be soldered to the correct pads in lieu of an external DC Jack. Be sure to place electrical tape across the battery to insulate it from the bottom of your PCB to prevent the possibility of shorting. Finally, screw the assembly together and fully test, prior to capturing the final frames of your project video.

Finally, be sure to address ALL issues from previous submissions and update your Table of Contents before attaching DER.docx to an email to handin under the Subject Line: A Counting Circuit (Complete)

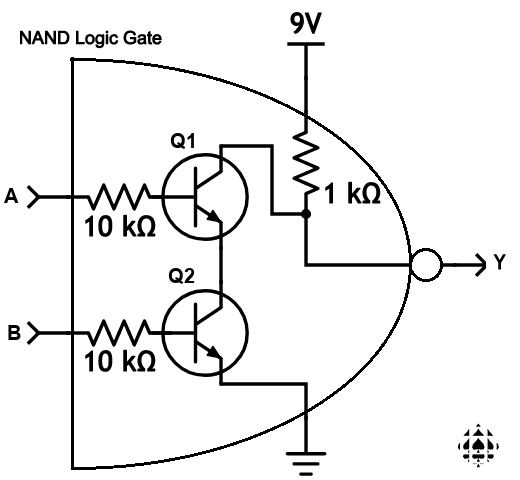

Project 1.2. NAND: The Universal Gate

Exploring the lower and lowest levels of any concept provides you with insights and capabilities for superior performance at the higher levels. Our Session 3 examination of transistors and logic gates has introduced you to a relatively fundamental level of computer technology that will serve to inform your future studies in this area. This project gives you a hands-on opportunity to solidify your knowledge and skills.

Exploring the lower and lowest levels of any concept provides you with insights and capabilities for superior performance at the higher levels. Our Session 3 examination of transistors and logic gates has introduced you to a relatively fundamental level of computer technology that will serve to inform your future studies in this area. This project gives you a hands-on opportunity to solidify your knowledge and skills.

Finally, before you begin reading this project description, I want you to challenge yourself. To THINK and do some research. Engineering requires concentration, focus, and discipline. If you can bring these skills to bear on your prototype, and ensuing Report, you'll experience a deep feeling of personal satisfaction unlike few others. The alternative is to take a superficial approach, casually guessing at what might work, blowing parts that are not easily replaced, or simply leaning too heaviliy on your smarter peers to get you across the finish line. This is like eating junk food in that you might experience a brief rush of having finished, but also a quick return to that empty feeling of a wasted opportunity to put another strong block in your solid engineering foundation. You'll have to decide.

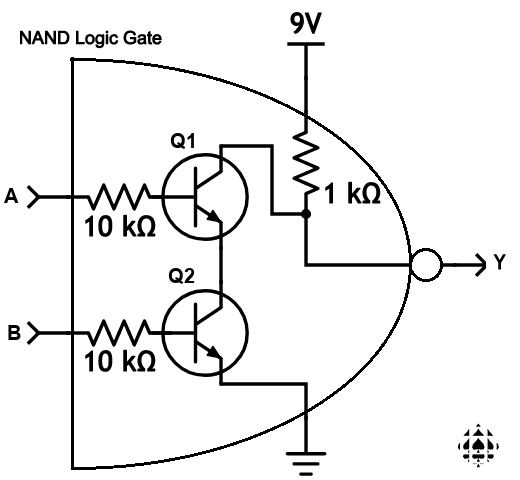

for 2020/2021. Our Inside Gates worksheet confirmed that the results of two-input NAND logic can be represented with two NPN transistors in series, in a pull up resistor configuration.

for 2020/2021. Our Inside Gates worksheet confirmed that the results of two-input NAND logic can be represented with two NPN transistors in series, in a pull up resistor configuration.

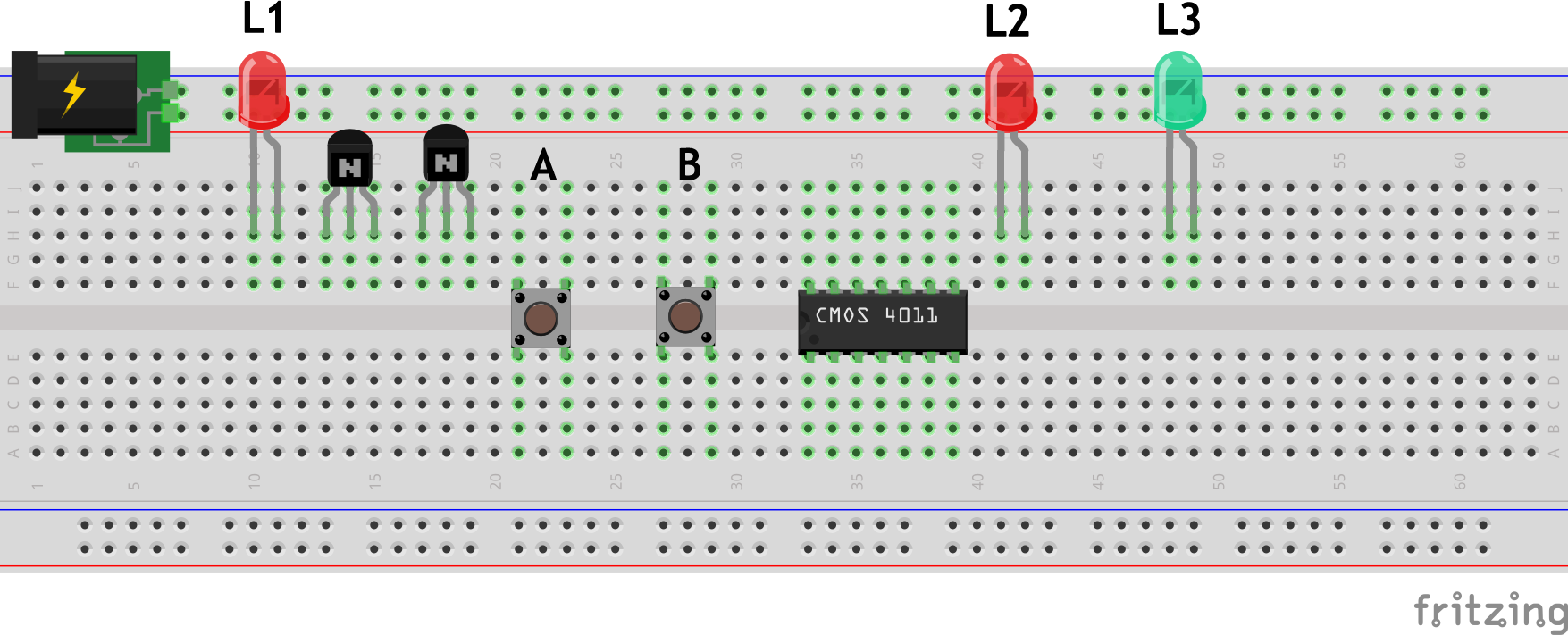

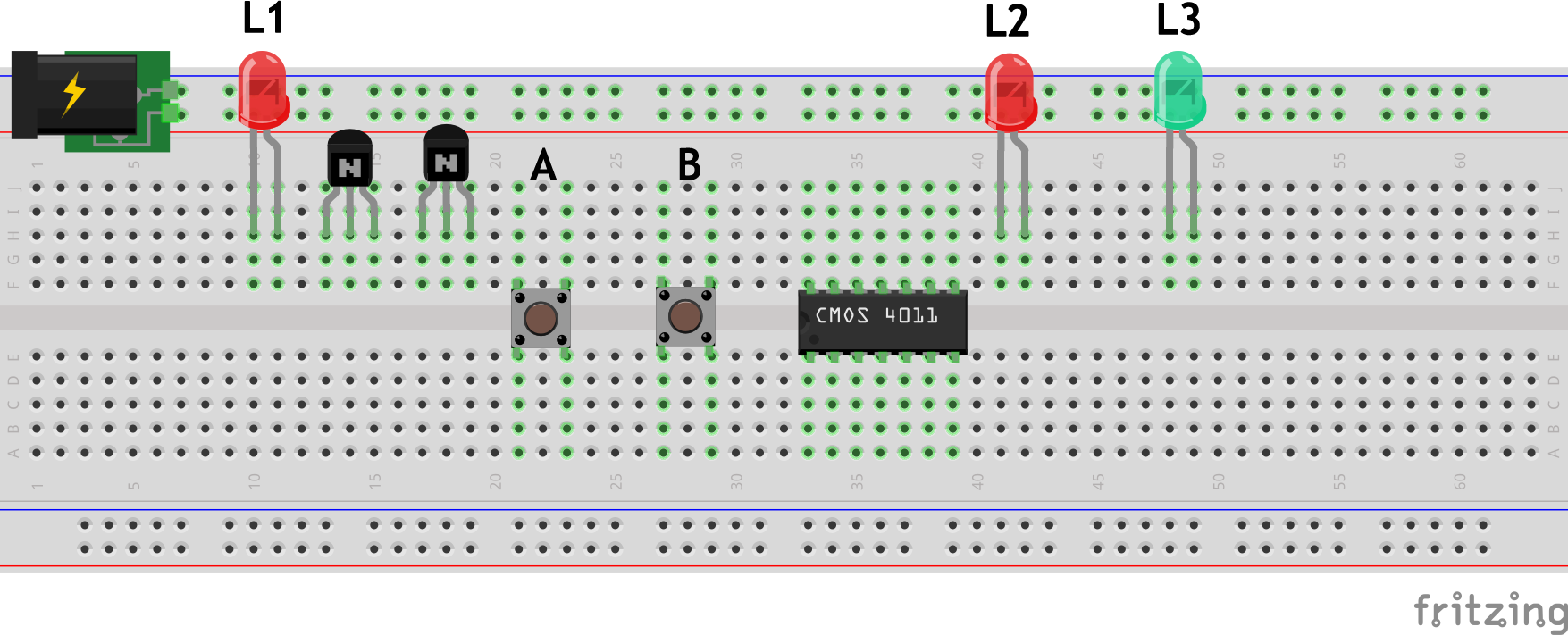

The purpose of this project is to confirm NAND's digital logic results in two ways: using the two analog NPN transistors to the left of the button inputs, and the CMOS 4011 digital logic IC to the right.

Task 1. On a single breadboard you are to assemble the major components shown below in roughly the positions indicated. The inputs to the circuit are two SPST momentary buttons (A and B), each one wired in a pulldown manner (use 4.7 kΩ resistors for the two pulldowns).The two outputs are the L1 and L2 red LEDs, each depicting the result of each NAND processor. Naturally, a successful conclusion will see the same output on each red LED for any of the four combinations of inputs (LL, LH, HL, HH)

The NAND gate is also referred to as the Universal Gate in that by wiring together one of more NAND gates, it is possible to achieve the same outputs as any of the other fundamental gates. You will research how to wire NAND gates to achieve each of the other logic results. Task 1 used only one of the four NAND gates on the CMOS 4011 IC. This gives us an opportunity to provide confirmation of NAND gate emulation of another logic operation, namely AND Logic.

Task 2. Using as many of the unused gates on the CMOS 4011 as necessary, wire the A and B inputs into the IC is such a fashion as to present the results of AND logic on the green LED , L3. If you have wired it correctly, the output on the green L3 should appear inverted from the red LEDs, L1 and L2. for every combination of button presses.

Attach your updated DER to an email to handin under the Subject Line: NAND: The Universal Gate no later than Saturday November 21, at midnight.

Project 1.1. The Capacitor Visualizer

Along with resistors, capacitors belong to a family of components known as passives in that they do not introduce a new source of energy into a circuit. Capacitors serve a number of useful functions in both DC and AC circuits. In completing this project you will strengthen your understanding that the capacitor (in series with a resistor), plays in the timing aspects of analog DC circuitry.

Along with resistors, capacitors belong to a family of components known as passives in that they do not introduce a new source of energy into a circuit. Capacitors serve a number of useful functions in both DC and AC circuits. In completing this project you will strengthen your understanding that the capacitor (in series with a resistor), plays in the timing aspects of analog DC circuitry.

This project takes time to undertake properly, so be patient, and start early.

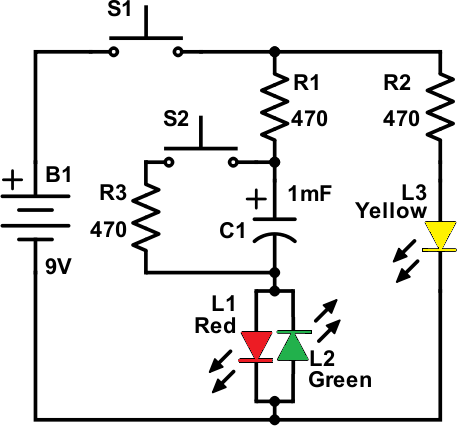

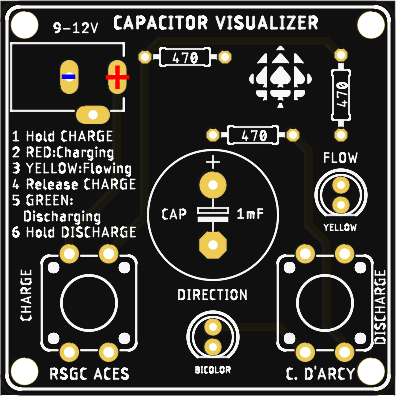

The schematic, below left, is of a test circuit that, in my view, best illustrates of the functional behaviour of an electrolytic capacitor in a DC circuit. You are familiar with the concept of a voltage divider from your first project. Looking at the junction (node) between S1, R1 and R2, we introduce the notion of a current divider as the current splits into two branches due to their parallel configuration.

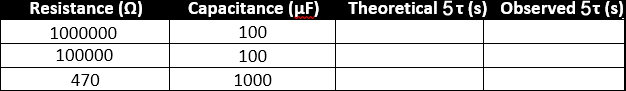

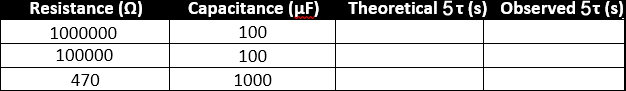

We have discussed the charging of an empty capacitor in terms of time constants and the effect this has on the capacitor in terms of its resistance (in AC circuits this property is referred to as reactance). In a DC circuit, a single RC Time Constant, denoted τ, can be expressed simply as,

`τ=R×C`

where τ is measured in seconds, R is measured in Ω, and C is measured in F. Also discussed in class (p. 32) is the expectation that after 5 RC time constants the capacitor is virtually fully charged (5τ~99%). One of the objectives of this project is to observe and confirm the expected results.

Task.

- Assemble a breadboard prototype from the schematic provided above, left, and test it throroughly to gain comfort. Now, since there are a limitless number of possible successful configurations the chances your first one was the best one are slim. As you begin to get more comfortable with how the circuis works, your need to interact with it and take a video of it, think deeply about how your breadboard prototype could be better arranged. This is the role of the designer. The prototype can ALWAYS be made better and more efficient.

- Now, onto the time experiments. To achieve the best results for each of the numerous time trials, the capacitor should be fully drained. In the Procedure section of your report, explain how this is achieved in the circuit.

- Within your working prototype use the first pair of resistor-capacitor values in the table below for R1 and C1. Connect the leads of the bicolor LED to the capacitor ground to ensure the color RED appears while C1 is charging. This ensures the orientation that agrees with the schematic. Note: Be sure to drain the capacitor and measure the voltage with your DMM to be sure. Explain this step in your Procedure and explain any related issues you have in achieving this.

- Once connected, hold the momentary button down (for as is required) before releasing it. Note the behaviour of the LEDs in particular, and try to explain what electrical behaviour at work, throughout. Do this a number of times until you feel you understand the principles.

- Now, more formally, using the timer on your phone, and through observation, record the approximate charging time for a fully discharged state until your eyes can no longer detect a visible state change in the red LED. A DMM can be used for more accurate results. Perform at least three trials with the first Resistor-Capacitor pair and record the average.

- For your DER, you are asked to duplicate the table that appears below. In the third column determine and enter the theoretical (expected) time to fill. In the fourth column, enter your observed result.

- Repeat Steps 3 and 4 for each of the remaining 2 RC pairs in the table. Again, perform a number of trials with each pair and record the average.

- In your DER, be sure to include the required sections listed above. It is up to you to decide the supporting images and graphics that engage your readers and leave them with a solid understanding of the concepts. The table above is large enough to be center-aligned on your page.

- Attach your DER to an email to handin under the Subject Line: The Capacitor Visualizer no later than Saturday October 24 at midnight.

There are no quizzes, tests, or exams in our ACES program. Put another way, you are NEVER put into the position of having a dramatically limited amount of time to demonstrate the skills you have acquired. You can invest as much (or as little) time into your reports as you choose. In return for being granted complete control over the depth and quality of your submissions I can place a premium on detail, precision, and the pursuit of perfection. So, my advice to you if you want to become exceptional is to follow the written and oral instructions carefully and, beyond the required elements of each report, demonstrate tasteful and appropriate creativity and imagination to distinguish yourself from the mediocre. Good luck and, remember, the race is long but it's over quickly.

There are no quizzes, tests, or exams in our ACES program. Put another way, you are NEVER put into the position of having a dramatically limited amount of time to demonstrate the skills you have acquired. You can invest as much (or as little) time into your reports as you choose. In return for being granted complete control over the depth and quality of your submissions I can place a premium on detail, precision, and the pursuit of perfection. So, my advice to you if you want to become exceptional is to follow the written and oral instructions carefully and, beyond the required elements of each report, demonstrate tasteful and appropriate creativity and imagination to distinguish yourself from the mediocre. Good luck and, remember, the race is long but it's over quickly. This final activity provides a simple introduction to fundamental capabilities of many digital devices: counting and display. There are a number of stages or subcircuits in this system and your DER will clearly present the role played by each.

This final activity provides a simple introduction to fundamental capabilities of many digital devices: counting and display. There are a number of stages or subcircuits in this system and your DER will clearly present the role played by each.