The ISR TIMER1_OVF_VECT can be used to trigger reporting of the fan's characteristics to the display module.

The ISR TIMER1_OVF_VECT can be used to trigger reporting of the fan's characteristics to the display module. Timer/Counter 1 Normal Mode 0: Overflow Interrupt

Reference: http://darcy.rsgc.on.ca/ACES/Datasheets/ATMEGA328P.pdf#page=111

Purpose: As a low-level replacement for <TimerOne.h> an internally generated periodic interrupt from Timer/Counter 1, in Normal mode, can act as a scheduler.

Filename: Timer1NormalOverflow.S

The ISR TIMER1_OVF_VECT can be used to trigger reporting of the fan's characteristics to the display module.

The ISR TIMER1_OVF_VECT can be used to trigger reporting of the fan's characteristics to the display module.

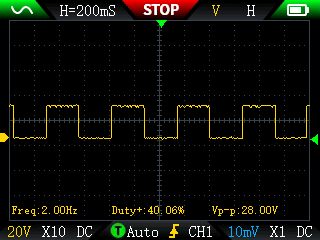

The frequency of the overflow, fOVF, depends on the frequency of the clock, fCLK, the capacity (in bits) of the Timer, CAP, and the prescaler, PS. The formula, in Hz, is expressed as, fOVF = fCLK/CAP/PS.

For example, Timer/Counter 1 (16 bits), configured in Normal Mode 0, running on the Nano with a clock speed of 16 MHz prescled by 64 would yield an overflow frequency of 16000000/65536/64 or approximately, 3.8 Hz.

If the interrupt service routine (ISR) simply toggled the Nano's onboard LED, the period of the blinking would be half of the interrupt frequency, or roughly 1.9 Hz. The scope capture to the right reflects these conditions (somewhat).