Mastering the Binary Number System continues to be one of the foundations of our ACES program. The online Cisco Binary Challenge, ported in 2017 to Studio Code's Binary Game, has fascinated ACES for years.

Mastering the Binary Number System continues to be one of the foundations of our ACES program. The online Cisco Binary Challenge, ported in 2017 to Studio Code's Binary Game, has fascinated ACES for years.Binary Challenge (Development Page) |

Mastering the Binary Number System continues to be one of the foundations of our ACES program. The online Cisco Binary Challenge, ported in 2017 to Studio Code's Binary Game, has fascinated ACES for years.

Mastering the Binary Number System continues to be one of the foundations of our ACES program. The online Cisco Binary Challenge, ported in 2017 to Studio Code's Binary Game, has fascinated ACES for years.

One bizarre issue with Studio Code's implementation is that it includes 256. Someone may wish to contact the author on that point.

Attempts to create a handheld device capable of similar functionality have been the subject of numerous student ISPs.

Binary Game (2018)

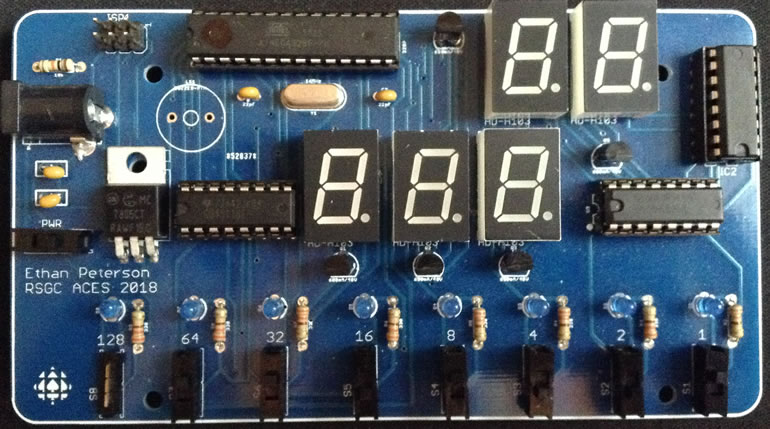

In 2018, Ethan Peterson (ACES '18) came close to finishing the task for his Long ISP. Based on the ATmega328P Ethan challegned himself to develop the code exclusively in AVR Assembly.

In 2018, Ethan Peterson (ACES '18) came close to finishing the task for his Long ISP. Based on the ATmega328P Ethan challegned himself to develop the code exclusively in AVR Assembly.

Alas, graduation presented itself before he could finish.

Binary Challenge (2019)

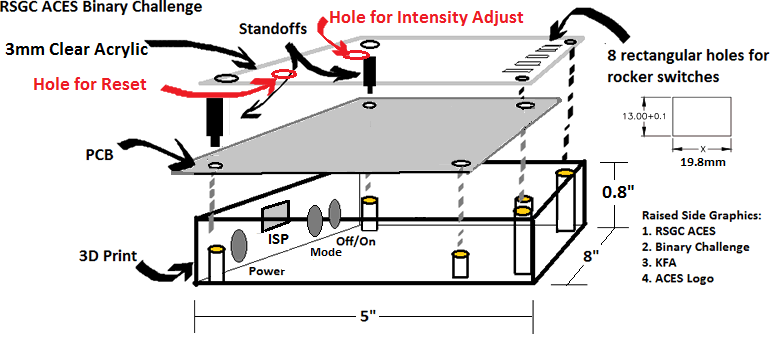

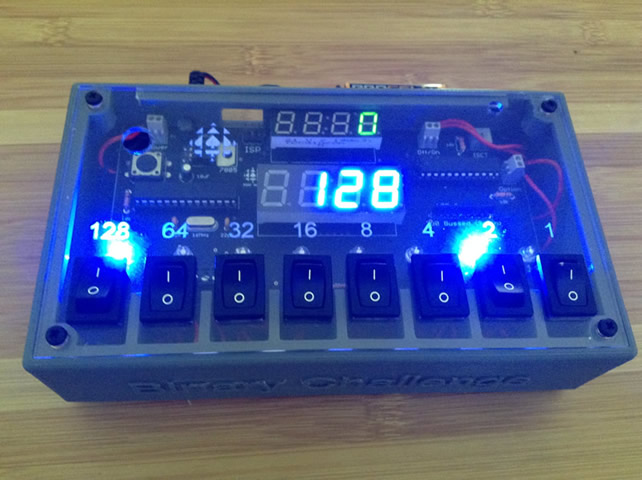

A second successful year with the Grade 5 introduction to the binary number system and digital logic gates has inspired me to finish what Ethan started. K. Fiset-Algarvio and I partnered in the design of the case. With any luck Jr. and Sr. ACES will reap the benefits of a class set of these devices starting in the fall of 2019. That's the goal anyway...

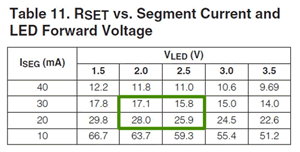

To extend the value and challenge of the experience to Grade 11 and 12s, modes covering hexadecimal and signed integers over the range from [-128,127] require a quad display. Thus two quad displays (Value and Score) require a 8 seven-segment displays to be driven; a task perfect for the MAX7219CNG CC display driver IC (assumnig we can reduce its susceptibility to noise).

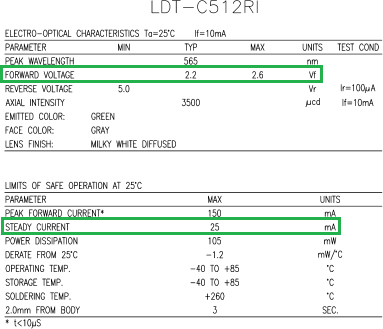

Possible Display Specs/Options

4-digit 7 Segment

4-digit 7 Segment LED Indicators

LED Indicators

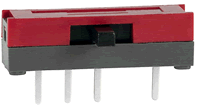

Switch Options

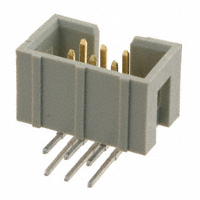

Shrouded ISP Connector

Shrouded ISP Connector

PCB Connectors

DC Jack

Pot (Intensity)

Software Features

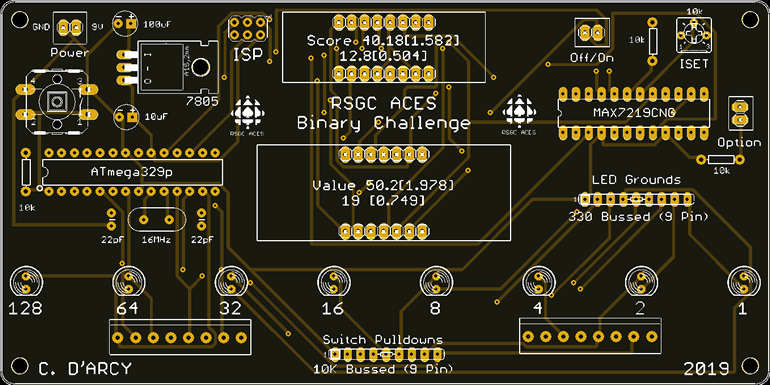

PCB Version 1

Version 1 sent to JLCPCB on 2019 06 04. 5 pcs. Update: PCB received on 2019 06 13. Soldered up and functional. Not without issues however. The MAX7219 is a very noisy IC and shuts down down the circuit consistenly after a few minutes. I've added decoupling caps across its supply pins in the hope this fixes the issue. Note: The same issue was observed with the scrolling message board until Ethan M. added caps as well.

2019 06 15: Version 1 Prototype Results

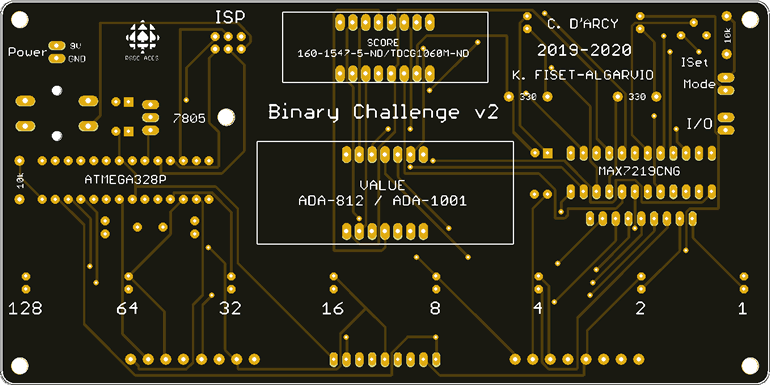

PCB Version 2

Version 2 edits included relocation of terminal headers to accommodate wire access from the gap in the sides. The ISP header was converted to right angle access from the back through a shrouded header. sent to JLCPCB on 2019 07 02. 30 pcs.

Upon receipt it turned out JLC forgot to drill out the four corner holes :( Click on image to the right to see the issue.

Some credit (coupon) for the oversight was provided by JLC and the order was resent on 2019 07 25 (requested gold plating) and received on 2019 08 06.

The corected V2 version was soldered up during PD week ...

Encasement